[ad_1]

I processori informatici automobilistici stanno rapidamente adottando nodi di processo avanzati. NXP ha annunciato lo sviluppo di processori automobilistici a 5 nm nel 2020 [1]Mobileye ha annunciato EyeQ Ultra utilizzando la tecnologia a 5 nm durante il CES 2022 [2]e TSMC ha annunciato i suoi processi “Auto Early” a 3 nm nel 2023 [3]. In passato, l’industria automobilistica era lenta nell’adottare le più recenti tecnologie dei semiconduttori a causa di problemi di affidabilità e della mancanza di esigenze impellenti. Non più.

L’uso di processi avanzati richiede l’uso di packaging avanzati come visto nel calcolo ad alte prestazioni (HPC) e nelle applicazioni mobili perché [4][5]:

- Sebbene la densità dei transistor sia aumentata vertiginosamente, la densità di I/O non è aumentata in modo proporzionale e frena la riduzione delle dimensioni dei chip.

- I processori dispongono di blocchi eterogenei e specializzati per supportare i carichi di lavoro odierni.

- Le dimensioni massime dei chip sono limitate dal rallentamento del ridimensionamento dei transistor, dai limiti del fotoreticolo e dalle rese inferiori.

- I miglioramenti del costo per transistor sono rallentati con i nodi avanzati.

- La memoria DRAM (Dynamic Random Access Memory) fuori dal package limita la larghezza di banda della memoria.

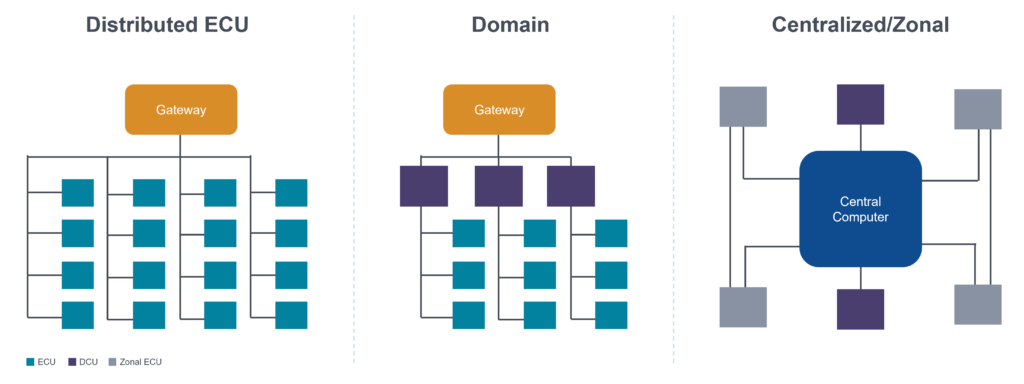

Questi sono stati i driver per l’utilizzo di pacchetti avanzati come il fan-out nei dispositivi mobili e 2.5D/3D nell’HPC. Inoltre, questi fattori si stanno lentamente ma inesorabilmente manifestando nelle unità di calcolo automobilistiche anche in una varietà di architetture automobilistiche (Figura 1).

Le architetture elettriche/elettroniche (E/E) dei veicoli si sono evolute da oltre 100 unità di controllo elettronico distribuito (ECU) a oltre 10 unità di controllo di dominio (DCU) [6]. L’architettura più recente introduce ECU zonali o di zona che sono raggruppate in posizioni fisiche nelle automobili e si collegano a potenti unità di calcolo centrali per l’elaborazione. Queste architetture più recenti migliorano la scalabilità, i costi e l’affidabilità dei veicoli definiti dal software (SDV) [7]. I processori in ciascuna di queste architetture sono più complessi di quelli della generazione precedente.

Più telecamere, radar, lidar, sensori a ultrasuoni e altro ancora alimentano i dati nelle unità di calcolo. L’elaborazione e l’inferenza di questi dati richiedono blocchi funzionali specializzati sul processore. Ad esempio, il system-on-chip (SoC) Tesla Full Self-Driving (FSD) HW 3.0 dispone di unità di elaborazione centrale (CPU), unità di elaborazione grafica (GPU), unità di elaborazione di rete neurale, Low-Power Double Data Rate 4 ( LPDDR4) e altri blocchi funzionali, tutti integrati su un unico pezzo di silicio [8]. Allo stesso modo, Mobileye EyeQ6 ha blocchi funzionali di cluster CPU, cluster di acceleratori, GPU e un’interfaccia LPDDR5 [9].

Man mano che verranno introdotti più blocchi funzionali, la dimensione e la complessità del chip continueranno ad aumentare. Invece di un singolo chip di silicio monolitico, un approccio chiplet con blocchi funzionali separati consente il riutilizzo della proprietà intellettuale (IP) insieme a nodi di processo ottimali per ciascun blocco funzionale [10]. Inoltre, pezzi di silicio di grandi dimensioni e monolitici costruiti con processi avanzati tendono ad avere problemi di resa che possono essere superati anche utilizzando chiplet.

Le attuali applicazioni dei sistemi avanzati di assistenza alla guida (ADAS) richiedono una larghezza di banda DRAM inferiore a 60 GB/s che può essere supportata con soluzioni standard Double Data Rate (DDR) e LPDDR. Tuttavia, ADAS Livello 4 e Livello 5 avranno bisogno di una larghezza di banda di memoria fino a 1024 GB/s che richiederà l’uso di soluzioni come Graphic DDR (GDDR) o High Bandwidth Memory (HBM) [11][12].

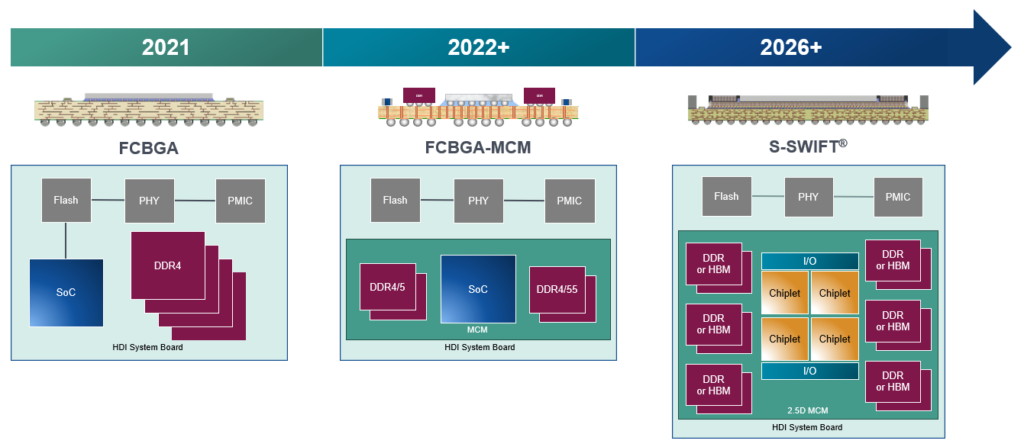

I processori automobilistici utilizzano pacchetti FCBGA (flip-chip ball grid array) dal 2010. FCBGA è diventato il pilastro di diversi SoC automobilistici come EyeQ di Mobileye, Tesla FSD e NVIDIA Drive. Le applicazioni consumer degli imballaggi FCBGA sono iniziate intorno al 1995 [13], pertanto ci sono voluti più di 15 anni perché questo pacchetto venisse adottato dall’industria automobilistica. Anche le unità di calcolo sotto forma di moduli multichip (MCM) o system-in-package (SiP) sono utilizzate nel settore automobilistico dall’inizio degli anni 2010 per i processori di infotainment. È probabile che l’uso degli MCM aumenterà nell’informatica automobilistica per consentire a componenti come SoC, DRAM e circuiti integrati di gestione dell’alimentazione (PMIC) di comunicare tra loro senza inviare segnali fuori dal pacchetto.

Man mano che le automobili si spostano verso un’architettura informatica centrale, i SoC diventeranno più complessi e dovranno affrontare sfide in termini di dimensioni e costi. La suddivisione di questi SoC in chiplet diventa una soluzione logica e diventa necessario confezionare questi chiplet utilizzando pacchetti fan-out o 2.5D. Proprio come FCBGA e MCM sono passati alle applicazioni non automobilistiche nel settore automobilistico, così faranno il fan-out e il packaging 2.5D per i processori informatici automobilistici (Figura 2). L’industria automobilistica è cauta, ma i cambiamenti dell’architettura sopra menzionati stanno spingendo verso un’adozione più rapida di pacchetti avanzati. Materiali, processi e controlli di fabbrica sono considerazioni chiave per la qualificazione di successo di questi pacchetti nelle applicazioni informatiche automobilistiche.

In sintesi, l’industria automobilistica sta adottando tecnologie avanzate di semiconduttori, come i processi a 5 e 3 nm, che richiedono l’uso di packaging avanzato a causa delle limitazioni nella densità di I/O, nelle riduzioni delle dimensioni dei chip e nella larghezza di banda della memoria. I processori nelle più recenti architetture E/E dei veicoli sono più complessi e richiedono blocchi funzionali specializzati per elaborare i dati provenienti da più sensori. Man mano che le automobili si spostano verso l’architettura informatica centrale, i SoC diventeranno più complessi e si troveranno ad affrontare sfide in termini di dimensioni e costi. La suddivisione di questi SoC in chiplet diventa una soluzione logica e diventa necessario il confezionamento di questi chiplet utilizzando la tecnologia fan-out o 2.5D.

Nota dell’editore: questo articolo è apparso per la prima volta nell’Annuario 3D InCites del 2024. Leggi l’intero numero qui.

Riferimenti

[1] NXP. “NXP sceglie il processo a 5 nm di TSMC per la piattaforma automobilistica ad alte prestazioni di prossima generazione”. NXP.

[2] Mobileye. “Mobileye al CES 2022.” Mobileye.

[3] Filo aziendale. “TSMC presenta i nuovi sviluppi tecnologici al simposio tecnologico del 2023.” Filo aziendale.

[4] Swaminathan, Raja. “Packaging avanzato: abilitare la prossima frontiera della legge di Moore attraverso l’integrazione eterogenea.” HotChips33.

[5] Semianalisi. Semianalisi “Packaging avanzato Parte 1”.

[6] McKinsey & Company. “Prepararsi per l’architettura EE di prossima generazione con il calcolo zonale.” McKinsey & Company.

[7] NXP. “Come le architetture E/E zonali con Ethernet stanno abilitando i veicoli definiti dal software.” NXP.

[8] WikiChip. “Chip Tesla (azienda automobilistica)/FSD.” WikiChip.

[9] Mobileye. “Chip EyeQ.” Mobileye,.

[10] Ziadeh, Bassam. “Stimolare l’adozione di imballaggi IC avanzati nelle applicazioni automobilistiche.” Presentazione all’IMAPS DPC, marzo 2023. General Motors, Fountain Hills AZ, 16 marzo 2023.

[11] K Matthias Jung e Norbert Wehn. “Guidare contro il muro della memoria: il ruolo della memoria per la guida autonoma”. Fraunhofer IESE, Kaiserslautern, Germania, e Gruppo di ricerca sulla progettazione di sistemi microelettronici, Università di Kaiserslautern, Kaiserslautern, Germania. Kluedo.

[12] Micron. “Cinco de Play: Memoria: è fondamentale per la guida autonoma?” Micron.

[13] McKinsey & Company. “Imballaggio avanzato dei chip: come i produttori possono giocare per vincere.” McKinsey & Company.

[ad_2]

Source link