[ad_1]

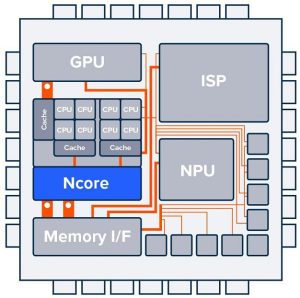

“Nel 2020, Arteris ha annunciato una partnership con Arm e l’allineamento delle nostre tabelle di marcia per supportare la sicurezza CHI-E e ASIL B e ASIL D”, ha dichiarato Arteris a Electronics Weekly. “Confermiamo l’espansione di tale partnership con una pre-convalida della nostra proprietà intellettuale di interconnessione Ncore con i core Armv9. Ncore è pronta a soddisfare i requisiti ISO 26262 da ASIL B a ASIL D per il settore automobilistico e altri sistemi mission-critical”.

CHI-E è un’interfaccia agente completamente coerente per i bus AMBA e si unisce alle interfacce CHI-B e ACE in Ncore. Sono inoltre disponibili ACE-Lite per la coerenza IO e AXI. “Sebbene AXI non disponga di segnali per la coerenza IO, Ncore consente ad AXI di leggere e scrivere da e verso le cache della CPU come se fossero coerenti IO”, ha affermato Arteris.

Aggiornate in Ncore v3.6 sono le policy di sostituzione per le cache, che ora includono PLRU (pseudo utilizzato meno di recente) e NRU (utilizzato non di recente).

Le interfacce di debug sono state aggiornate a AMBA APB4 e il controllo di sicurezza funzionale di Ncore ora supporta i bit di parità che proteggono i registri.

Sono supportate SRAM multiciclo ed è presente una quarta rete di controllo per migliorare la larghezza di banda in lettura e scrittura.

“I progettisti di SoC devono affrontare la crescente complessità derivante dal numero di elementi di elaborazione, protocolli multipli e requisiti di sicurezza funzionale dell’elettronica moderna”, ha affermato Charles Janac, CEO di Arteris. “La nostra ultima versione di Ncore segna un’importante pietra miliare verso la nostra visione finale di connettere qualsiasi processore, utilizzando qualsiasi protocollo e topologia”.

La pagina del prodotto Ncore può essere trovata qui.

[ad_2]

Source link