[ad_1]

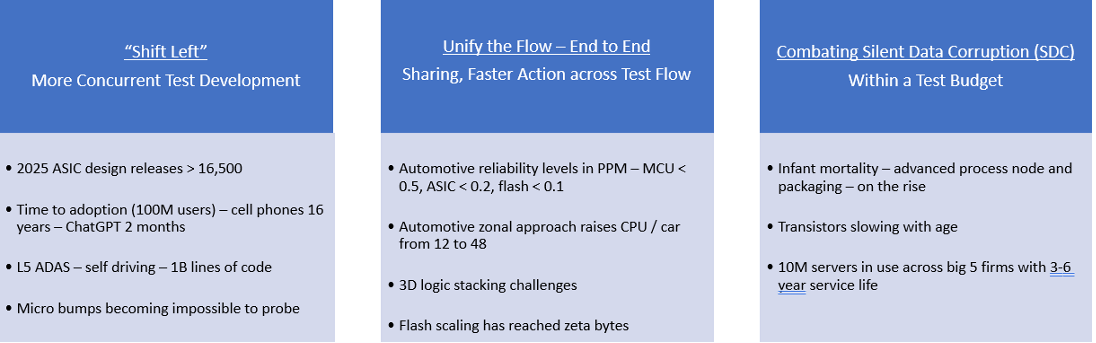

Il test dei dispositivi a semiconduttore non ha valore aggiunto? Certamente alcuni aspetti restano immutabili. Il test è uno dei tre mezzi per garantire le parti oltre alla caratterizzazione e alla progettazione stessa. Dato il contesto di mercato – nel settore automobilistico, informatico e del packaging avanzato – sono emerse nuove sfide di test e valore aggiunto. Tre temi principali sono lo “spostamento a sinistra”, ovvero la necessità di uno sviluppo più simultaneo con dipendenze sempre crescenti tra progettazione, confezionamento, test e operazioni sul campo; maggiore unificazione nello sviluppo, nella produzione e nel flusso di test end-to-end; e la continua guerra alla corruzione silenziosa dei dati (SDC), bilanciata dall’economia dei test (Figura 1).

Cos’è lo spostamento a sinistra?

Il termine “Shift Left” è stato utilizzato sempre più spesso nell’ambito dello sviluppo per indicare attività che una volta venivano eseguite in sequenza ma che ora devono essere eseguite contemporaneamente. Ciò è solitamente dovuto al rafforzamento delle dipendenze tra le attività. Diversi tipi di approcci di “progettazione per…” stanno prendendo piede come strumenti all’interno di un più ampio ombrello di progettazione per test (DFT): S (stress), R (affidabilità), I (ispezione) e O (osservabilità). Al di là dei test, alcune aziende automobilistiche utilizzano S (sicurezza) e S (sicurezza).

Nei prodotti più semplici la sonda per wafer era un mezzo accettabile per determinare il Known Good Die (KGD) come schermo grossolano prima dell’assemblaggio. Ora c’è troppo valore in un modulo SiC da 8 FET [1] o moduli multichip di elaborazione 2.5/3D come system-in-package (SiP) e chiplet. La sonda deve produrre il più vicino possibile a KGD. Con molte forme di packaging avanzato, tutte le interconnessioni devono essere controllate indipendentemente dall’accessibilità, da qui il termine stack a buono noto (KGS) e sistema a buono noto complessivo (KGS).

La specifica Universal Chiplet Interconnect Express (UCIe). [2], mirato al die-to-die, è stato aggiornato alla versione 1.1 per affrontare più protocolli e modelli di utilizzo più ampi. Poiché l’impilamento degli stampi 3D si evolve dalla memoria HBM (High Bandwidth Memory) alla logica, si presentano nuove sfide soprattutto quando si utilizza la logica da vari nodi di processo. Un esempio sono i nuovi meccanismi di stress fisico e una maggiore probabilità di guasti alle interconnessioni.

La specifica IEEE 1838 per gli stack die-to-die è un altro esempio di uno “spostamento a sinistra” nell’avvicinare progettazione e test. KGx inizia con l’architettura e la pianificazione del prodotto, deve essere supportato dalla progettazione e viene fornito tramite operazioni di test e assemblaggio.

Flussi di test più complessi e distinte base (BoM) più costose richiedono una maggiore unificazione del flusso di test end-to-end per lo sviluppo e l’azione in produzione.

Il collegamento tra apparecchiature di test automatizzato (ATE) e test a livello di sistema (SLT) mostra un enorme aumento della necessità di SLT dopo il test ATE. SLT può essere fino a 50-100 volte meno costoso di ATE, ma storicamente è stata un'”isola” che utilizza algoritmi molto diversi e lunghi (si pensi a 20 minuti) che riflettono i casi d’uso del cliente finale.

Intel rileva che molti dei suoi clienti utilizzano SLT per periodi molto più lunghi rispetto all’azienda. Molti progressi di Teradyne e Advantest facilitano più feed-forward e feedback dei modelli di test dai due ambienti per ottenere risultati iniziali di sviluppo dei test in tempi di reazione migliorati per migliorare il test ATE a monte quando compaiono nuove modalità di guasto su SLT. Altri esempi includono l’esecuzione di ulteriori analisi sul tester al volo. I vantaggi di ciò includono test adattivi. Ad esempio, se un dato lotto di materiale (wafer, prodotti finiti) presenta determinati parametri attorno agli angoli del processo (transistor veloci/lenti, alta/bassa potenza), il programma di test può essere variato in modo adattivo e dinamico. I produttori di ATE hanno inserito più di questi strumenti all’interno del tester per il processo decisionale in tempo reale, invece di un computer centrale del banco di prova.

All’IEEE ITC dell’ottobre 2023, Cariad (il ramo elettronico di Volkswagen) ha sottolineato che i test per gli ambienti ADAS L4 e L5 generano molti dati che, al momento, rappresentano un’opportunità persa di analisi/azione. L’unificazione dei test ATE eliminerebbe le sovrapposizioni e le duplicazioni derivanti dal modo in cui i test venivano storicamente eseguiti, con batterie di test provenienti da silos di ricerca e sviluppo, garanzia di qualità, sicurezza e organizzazioni di prodotto/test/progettazione.

Possiamo eliminare la corruzione silenziosa dei dati?

Tutti questi progressi nei test e nell’unificazione sono positivi, ma perché si verificano ancora corruzioni dei dati molto subdole e silenziose (SDC) sul campo? La risposta è più sperimentale? Rimangono silenziosi e anche se il meccanismo viene scoperto, ulteriori test comportano costi aggiuntivi.

All’IEEE ITC 2023 si è svolto un eccellente dibattito sulla DSC su come individuarli nella produzione, creare modelli avanzati di difetti, migliorare lo screening e i vantaggi della telemetria. Nel complesso, sono state evidenziate due cause principali: i vecchi difetti di punti casuali vecchio stile e guasti di tipo parametrico più sistemici all’interno di progetti complessi.

I difetti puntuali possono essere fughe di test al tempo zero o difetti che richiedono solo un po’ di tempo di “attivazione” per emergere. È possibile ricorrere a test ad alta tensione più “intelligenti”? Gli esempi più sinistri, sebbene di natura parametrica, comportano effetti di ritardo molto piccoli e/o cadute di tensione in situazioni e schemi di alimentazione complessi. Sorge la domanda: si può fare di più nella progettazione/convalida per coprire i carichi di lavoro dei circuiti integrati adeguati? Più specificamente, se si dice che una parte è “passata” o “fallita”, allora è necessario comprendere l’intera condizione impostata, ovvero: a quale frequenza e a quale tensione? È necessario un approccio multilivello. È opportuno ripristinare i test/le impronte digitali sulla corrente di riposo? Ma dopo tutti questi sforzi, troveremo semplicemente i meccanismi facili e quelli difficili continueranno a sfuggirci?

In sintesi, i fattori trainanti del settore, come l’automotive, l’informatica e i nodi di processi/pacchetti avanzati; combinato con la ricerca infinita di essere più piccoli, migliori, più veloci e più economici, continuano a comportare nuove sfide di test. È necessario un maggiore “spostamento a sinistra” nei test per accelerare e migliorare la qualità dello sviluppo. Standard come IEEE 1838 e UCIe 1.1 sono passi nella giusta direzione. Si sta verificando una maggiore unificazione nel flusso del processo di test, incluso il collegamento più stretto dei test SLT e ATE e lo spostamento di più analisi “al volo” al tester per una reazione in tempo reale. Infine, il problema della DSC è in aumento ed è molto difficile risolverlo in modo economicamente vantaggioso.

[1] “Sfide dei MOSFET SiC, domanda e industrializzazione di test e burn-in” – Mark Berry, 3D InCites, [2] “Aggiornamento su UCIe” – Mark Berry, 3D InCites, ottobre 2022novembre 2022

Questo articolo è apparso originariamente nell’Annuario 3D InCites del 2024.

[ad_2]

Source link