[ad_1]

TSMC ha recentemente introdotto la sua “3DFabric Alliance”, come parte della sua Open Innovation Platform (OIP), per aiutare i clienti ad affrontare le sfide della complessità della progettazione a livello di sistema e di semiconduttori. L’intenzione è quella di ottenere una rapida implementazione della progettazione per applicazioni HPC e mobili di prossima generazione utilizzando le tecnologie “3DFabric™” di TSMC.

Nello specifico l’azienda elenca i suoi obiettivi come:

- Accelera l’innovazione e la preparazione dell’ecosistema 3DFabric

- Accelera l’adozione e la produzione di 3DFabric da parte dei clienti

- Guida il settore nella progettazione di sistemi integrando la logica avanzata con le tecnologie 3DFabric per fornire una gamma completa di soluzioni e servizi best-in-class per la progettazione di semiconduttori, moduli di memoria, tecnologia dei substrati, test, produzione e confezionamento.

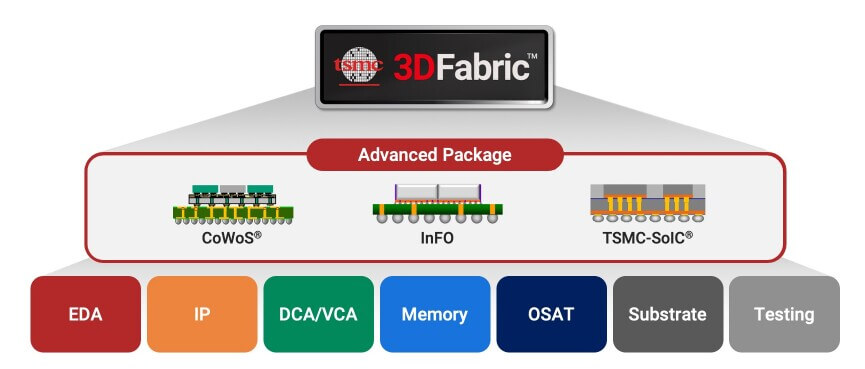

Secondo l’azienda, “l’impilamento 3D del silicio e le tecnologie avanzate di packaging richiedono un’ampia collaborazione nell’ecosistema per aiutare i progettisti a percorrere il percorso migliore attraverso la miriade di opzioni e approcci a loro disposizione. Ecco perché TSMC ha lanciato la 3DFabric Alliance. Ciò si aggiunge alla partnership esistente con l’ecosistema OIP in EDA, IP, DCA, Cloud e VCA, che offre ai clienti un modo semplice e flessibile per sfruttare la potenza dell’IC 3D nei loro progetti utilizzando le tecnologie 3DFabric di TSMC, una famiglia completa di soluzioni 3D. impilamento del silicio e tecnologie di confezionamento avanzate”.

La 3DFabric Alliance lavorerà con i membri dell’alleanza nelle sette aree mostrate nella Figura 1 per fornire “…soluzioni e servizi per soddisfare le esigenze di progettazione di circuiti integrati 3D del cliente in tutte le fasi di progettazione rilevanti di strumenti e flussi EDA, IP e componenti di memoria, servizi di progettazione, così come così come i processi backend tra cui OSAT, substrato e test per consentire la consegna ai clienti di prodotti del sistema di qualità.

La famiglia di tecnologie 3DFabric di TSMC è costituita da tecnologie di interconnessione frontend e backend sia 2D che 3D. Le sue tecnologie front-end, o TSMC- System on Integrated Chips (SoIC®), utilizzano la precisione e le metodologie delle fabbriche di silicio di TSMC necessarie per l’impilamento del silicio 3D. Queste tecnologie includono l’impilamento di stampi Chip-on-Wafer (CoW) e Wafer-on-Wafer (WoW), per consentire l’impilamento 3D di stampi simili e dissimili per fornire:

- Maggiore potenza di calcolo aumentando il numero di core di calcolo

- Più memoria e larghezza di banda maggiore con memoria in stack

- Erogazione di potenza migliorata con condensatori a scavo profondo per applicazioni ad alta potenza

TSMC afferma di disporre anche di più fabbriche di backend dedicate che assemblano e testano gli stampi in silicio, compresi gli stampi 3D impilati, e li trasformano in dispositivi confezionati.

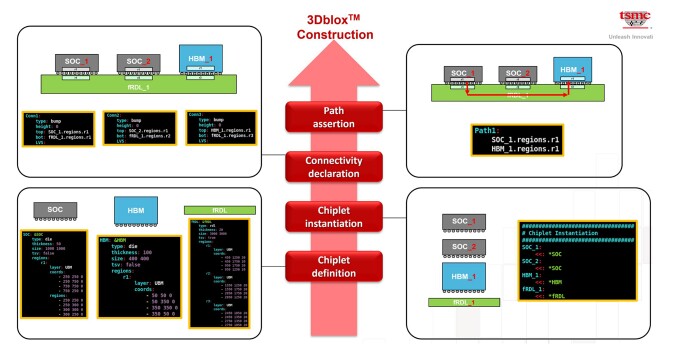

3Dblox

Lo standard aperto 3Dblox mira a modularizzare e ottimizzare le soluzioni di progettazione di circuiti integrati 3D per l’industria dei semiconduttori. 3Dblox è uno standard aperto che fornisce costrutti linguistici generici in grado di rappresentare tutte le strutture 3D-IC attuali e future. Modularizza le strutture 3D-IC in modo tale che gli strumenti EDA e il flusso di progettazione possano essere più semplici ed efficienti e garantisce che gli strumenti EDA standardizzati e i flussi di progettazione siano conformi alla tecnologia 3DFabric di TSMC.

TSMC ha inoltre lanciato il Comitato 3Dblox, organizzato come gruppo standard indipendente, per creare una specifica a livello di settore che consenta la progettazione di sistemi con chiplet di qualsiasi fornitore. Lavorando con membri chiave tra cui Ansys, Cadence, Siemens e Synopsys, il comitato ha dieci gruppi tecnici di argomenti diversi e propone miglioramenti alle specifiche e mantiene l’interoperabilità degli strumenti EDA. I progettisti possono ora scaricare le ultime specifiche 3Dblox dal sito web 3dblox.org e trovare ulteriori informazioni su 3Dblox e sull’implementazione del suo strumento da parte dei partner EDA.

Substrati

TSMC ha collaborato con successo con i partner dei substrati IBIDEN e UMTC per definire un file della tecnologia di progettazione del substrato per facilitare l’instradamento automatico del substrato per ottenere significativi vantaggi in termini di efficienza e produttività.

Test

TSMC sta collaborando con i partner ATE (Automatic Test Equipment) Advantest e Teradyne per risolvere una serie di sfide di test 3D per ridurre eventuali perdite di rendimento e migliorare l’efficienza di erogazione di potenza per i test sui chiplet. Per dimostrare l’accesso ai test ad alta velocità per i test dello stack 3D attraverso un’interfaccia funzionale, TSMC sta lavorando con Synopsys e i partner ATE su un dimostratore di silicio per raggiungere l’obiettivo di un aumento di 10 volte della produttività dei test. La Società sta inoltre collaborando con tutti i partner EDA design-for-test (DFT) per garantire test dell’interfaccia efficaci ed efficienti.

Per tutte le ultime novità su Advanced Packaging, restate collegati a IFTLE……….

[ad_2]

Source link