[ad_1]

Tutto dipende da chi parlerai a IEDM 2023. L’industria dei chip semiconduttori si sta muovendo in un nuovo regno che sarà basato sulla tecnologia chiplet, oppure l’industria sta continuando a portare avanti la tecnologia front-end e backend e le due tecnologie sono si stanno trasformando insieme per portare avanti la Legge di Moore nell’elaborazione avanzata come ha fatto negli ultimi 60 anni.

IEDM 2023 è stato il 69th riunione dell’IEEE Electron Devices meeting, e tutto è tornato a pieno ritmo. Dopo un paio d’anni di attività ibrida online e online, di persona, la conferenza è ora tornata a essere prevalentemente di persona, ma hanno un’opzione per rivedere le presentazioni videoregistrate, che consente a coloro che hanno più aree di interesse di tornare indietro e visualizzare le conferenza e rinfrescare la memoria quando scrivono della conferenza.

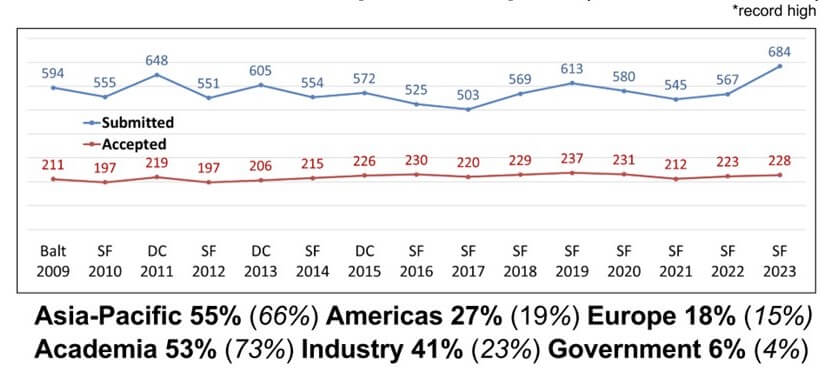

IEDM 2023 in numeri

Il focus della conferenza era Dispositivi per un mondo intelligente basati su 60 anni di CMOS. Sono stati presentati 684 documenti e 228 selezionati dai comitati. La ripartizione dei documenti accettati era del 53% accademica, del 41% dell’industria e del 6% delle istituzioni governative. Dal punto di vista accademico, una parte significativa della ricerca è finanziata da sovvenzioni governative, DARPA, SRC e altri.

Con tutte le discussioni sul Chips Act, è stato interessante vedere che il 55% dei documenti accettati provenivano dall’Asia Pacifico (AP), il 27% dagli Stati Uniti e il 18% dall’Europa. Il maggior numero di articoli di AP è una tendenza da diversi anni, ma in una certa misura riflette il fatto che AP si concentra in modo significativamente maggiore sulla ricerca e sviluppo avanzati sui semiconduttori rispetto a quanto avviene negli Stati Uniti. Sarà interessante vedere se l’aumento dell’attenzione sulla formazione sui semiconduttori finanziata dal Chips Act sposterà l’ago sui documenti pubblicati negli Stati Uniti e in Europa.

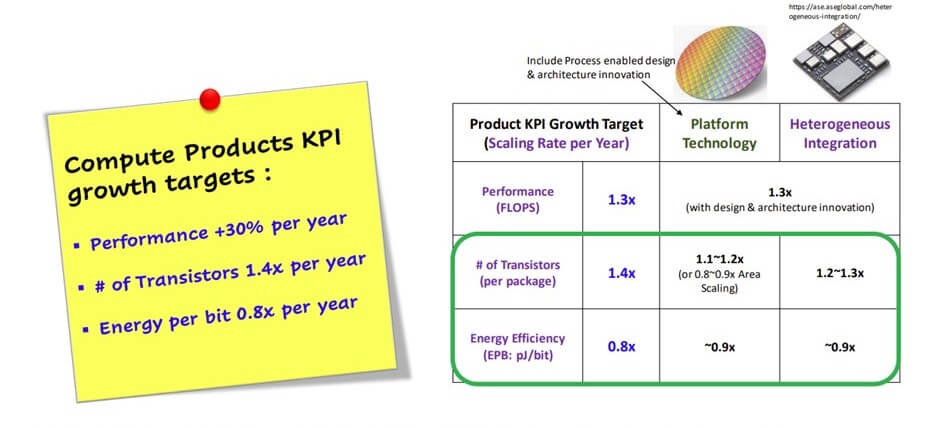

A IEDM, il mio obiettivo principale è capire dove sta andando l’avanguardia e come si propone che il settore ci arrivi. Mi fa sempre piacere quando i tecnici iniziano a farsi coinvolgere nel clamore di marketing sulla direzione che prenderà il settore. Mentre da un lato si parla di un trilione di dollari di entrate per l’industria dei semiconduttori, ora c’è un notevole clamore sul fatto che il settore raggiunga un trilione di circuiti integrati a transistor (IC). Attualmente, il SoC Apple M1 ha circa 117 miliardi di transistor e Intel Ponte Vecchio, che è un chiplet, ha 100 miliardi di transistor. Per raggiungere il numero di 1.000 miliardi di transistor sarà necessario un aumento di 10 volte nei prossimi anni. La domanda è: come arriva l’industria?

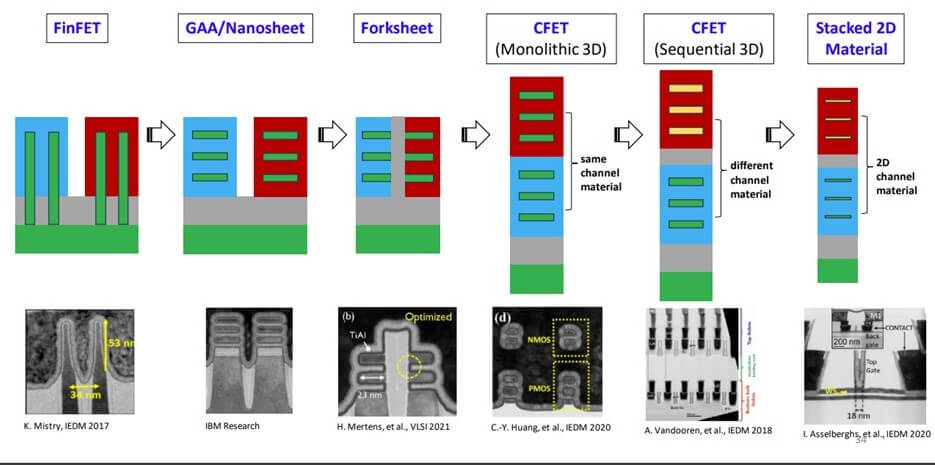

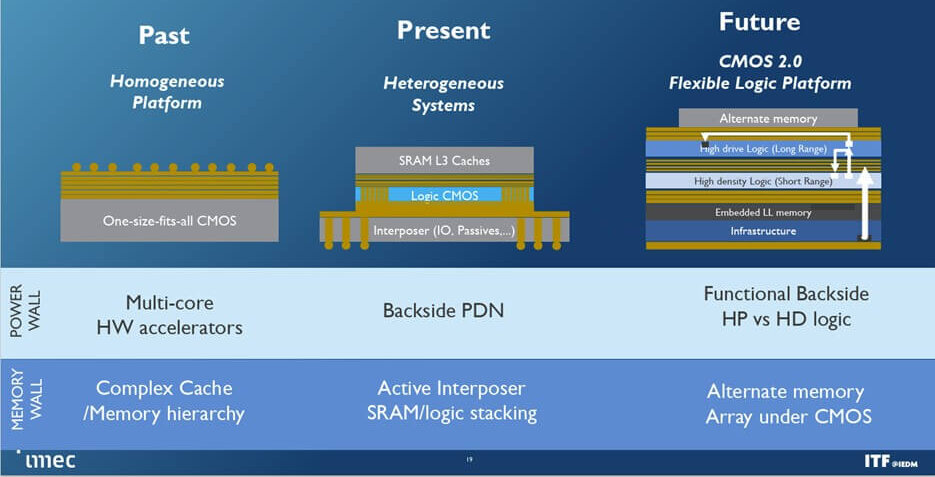

Dai documenti di IEDM, l’approccio sarà duplice. Si continuerà a migliorare la tecnologia dei chiplet per aumentare il numero di processori e memoria collocati insieme sullo stesso interpositore. L’altro è passare dall’attuale tecnologia finFET a Gate All Around, (GAA) alla tecnologia CFET monolitica fino a materiali con canali bidimensionali utilizzando il modello CFET. Jie Deng di Qualcomm ha sottolineato che oltre a integrare il CFET e la tecnologia di packaging, la tecnologia della piattaforma dovrà considerare come integrare al meglio tutto insieme per creare il sistema di prossima generazione in un pacchetto (SiP).

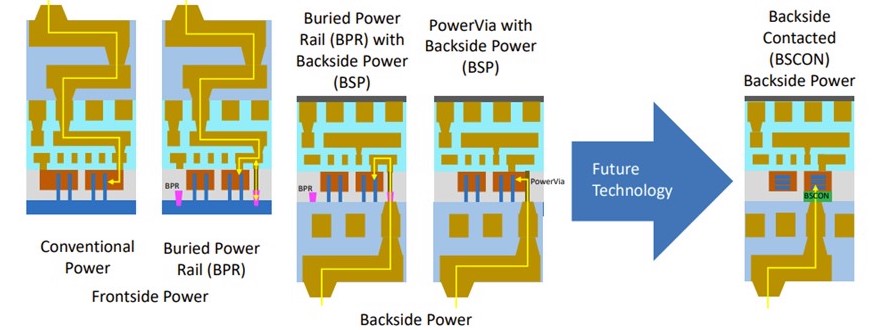

Mentre la tecnologia dei transistor si sta evolvendo per raggiungere un trilione di transistor, anche la tecnologia di interconnessione deve evolversi. Intel sta implementando l’erogazione di energia backside per migliorare le prestazioni di interconnessione e contribuire a ridurre la complessità dei processi. Si spera inoltre che l’implementazione dell’alimentazione posteriore contribuisca a ridurre il calore generato dai chip e dai chiplet, che è una delle questioni chiave da considerare nella progettazione del sistema. Soprattutto dal punto di vista della sostenibilità nei data center.

Una delle chiavi del successo dei chiplet è risolvere il muro di memoria. Questo problema è duplice:

- Cache SRAM di memoria integrata nel chip. Può continuare a ridursi alla stessa velocità del transistor logico e soddisfare i requisiti di velocità necessari per i processori del futuro? La MRAM incorporata sta emergendo come alternativa alla SRAM, il vantaggio è che la MRAM può essere incorporata nell’interconnessione e potenzialmente ridurre i requisiti di area del SoC o del Chiplet. Tuttavia, nelle conversazioni alla conferenza si è sentito parlare del vecchio, il miglior sostituto per SRAM è SRAM. Questo vale anche per DRAM e NAND flash, poiché si stanno ancora cercando alternative migliori.

- Implementazione DRAM di memoria a larghezza di banda elevata (HBM), che era un argomento caldo allo IEDM. Questa tecnologia sta avanzando rapidamente ma presenta ancora sfide nel trasferimento dei dati che generano calore. La Figura 5 mostra la versione IMEC della roadmap di integrazione eterogenea per la sfida della memoria integrata o nel chiplet.

Se si considera che storicamente ogni 2 anni l’industria ha raddoppiato il numero di transistor per unità di area, e che attualmente l’industria conta 100 miliardi di transistor su un SoC, e che anche la legge di Moore è stata leggermente ampliata per considerare il numero di transistor per superficie unitaria. Se l’industria mantiene il passo, il numero di transistor in un pacchetto chiplet dovrebbe superare i trilioni nel periodo 2028-2030. Dalle conversazioni all’IEDM, le chiavi per raggiungere questo successo sembrano essere lo stacking dei transistor, il miglioramento della densità di interconnessione e RC, e la ricerca di una soluzione al muro della memoria per ridurre la quantità di energia consumata e prodotta dai sistemi di il futuro. In questo momento scommetto di raggiungere un trilione di transistor prima di un trilione di dollari.

[ad_2]

Source link