[ad_1]

La risposta ovvia è un singolo microcontrollore con pochi pin, e questo è chiaramente possibile, ma farlo funzionare nei casi limite non è banale se l’obiettivo è una buona risoluzione, per evitare, ad esempio, sovra o sottocampionamento. .

Allora come realizzare un bel circuito analogico?

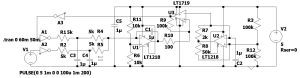

Bene, ecco il mio ultimo suggerimento (Giustomodellato in LTspice, ma non ancora testato IRL):

Bene, ecco il mio ultimo suggerimento (Giustomodellato in LTspice, ma non ancora testato IRL):

È basato sul feedback e forma un circuito bloccato PWM.

L’amplificatore operazionale rail-to-rail U2 è cablato come un oscillatore che genera, ai fini di questo circuito, una forma d’onda a dente di sega (in realtà ha bordi esponenziali anziché diritti, ma era abbastanza buono per il leggendario 555 – grazie signor Camenzind 🙂

R7 e C2 impostano la frequenza, quindi se è richiesta la variabilità della frequenza, C2 potrebbe essere sostituito da un set di condensatori 1:10:100 e un interruttore per l’impostazione della frequenza a passi di decade, e R7 potrebbe essere variabile per sintonizzarsi nei decenni.

L’aggiunta del comparatore rail-to-rail U3 al dente di sega di U2 produce un generatore PWM controllato in tensione il cui ingresso di tensione è l’ingresso non invertente di U3 e la cui uscita è l’uscita di U3.

Se un semplice potenziometro fosse collegato a questo ingresso, consentirebbe di produrre rapporti PWM controllati manualmente, alle frequenze impostate da R7 e C2.

U1 completa il ciclo, amplificando la differenza tra l’ingresso PWM e una copia invertita dell’uscita di U3 (in realtà, entrambi sono tramite inverter CMOS per assicurarsi che abbiano entrambi la stessa ampiezza).

L’output segue il ciclo di lavoro del 90% dell’input, con un leggero rimbalzo nella fase iniziale

L’output segue il ciclo di lavoro del 90% dell’input, con un leggero rimbalzo nella fase iniziale

La polarità del feedback è organizzata in modo che il rapporto mark-space all’uscita di U3 si insegua continuamente nel rapporto mark-space dell’ingresso (in alto a sinistra), indipendentemente dalle due frequenze.

Una volta stabilizzato (la traccia inizia dopo 50 ms), l’uscita (la frequenza più bassa in questo caso) traccia il ciclo di lavoro dell’ingresso (10% in questo caso)

Una volta stabilizzato (la traccia inizia dopo 50 ms), l’uscita (la frequenza più bassa in questo caso) traccia il ciclo di lavoro dell’ingresso (10% in questo caso)

Esistono molti inverter in quanto ciò consente di collegare l’ingresso non invertente del comparatore all’uscita di U1 (tramite il resistore di isteresi 100R R10) dove può causare pochi danni, piuttosto che alla giunzione di R7 e C2 dove il un altro resistore di isteresi (R9) potrebbe causare il jitter dell’oscillatore (affermo….).

C3 e C4 non sono necessari per il funzionamento del circuito.

Il circuito è costruito attorno a ciò che è emerso da una sfida personale un paio di anni fa: come sarebbe l’equivalente PWM di un rilevatore di fase.

La mia risposta (e potrebbe ancora essere sbagliata 🙂 era solo due resistori nella terra virtuale di un amplificatore operazionale, con segnali di uguale ampiezza e uno dei PWM invertito.

Ciò che fanno C3 e C4 è rallentare i cambiamenti di input in modo che l’amplificatore operazionale non abbia difficoltà a tenere il passo e il suo output sia meno disturbato.

La risposta non è rapida (è stata progettata per tenere traccia dei cicli di lavoro raramente modificati) ma il rapporto mark-space in uscita sembra finire molto vicino al rapporto mark-space in ingresso in un’ampia gamma di rapporti.

LTspice è stato utilizzato per modellare questo circuito di prova, quindi grazie ad ADI per aver continuato a mantenere questo software gratuito.

[ad_2]

Source link